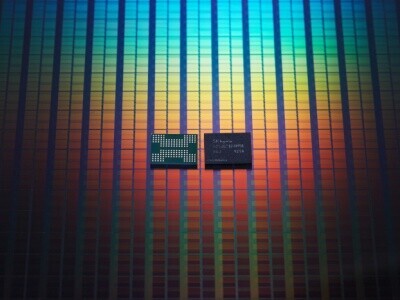

A Hynix még az előző év nyarán prezentálta 4D NAND jövőképét, az első termékük pedig múlt novemberben érkezett meg, amit most követ egy modernebb verzió. Az új, 1 terabbites konstrukció 128 cellaréteget használ, a cellák pedig három bitet tárolnak, azaz TLC-s megoldásnak tekinthető a memória.

A 4D elnevezés ezúttal se tévesszen meg senkit, a lapka valójában háromdimenziós struktúrájú azzal a kis trükkel, hogy a CMOS logika nem a cellák mellé, hanem alá van elhelyezve. Ez a PUC, azaz a Periphery Under Cell technológia, ami igazából még egyedinek sem számít, mivel a Micron és az Intel igen hasonló dizájnt használ a 3D NAND érában, csak az említett vállalatok erre CuA (CMOS under Array) néven utalnak, de egyébként a Samsung is ilyen irányba fejleszt.

Az új lapka az I/O tempó tekintetében 1400 Mbps-ot képes felmutatni, méghozzá 1,2 voltos feszültség mellett, így valamivel gyorsabb a fejlesztés az elődnél, de nem szignifikánsan.

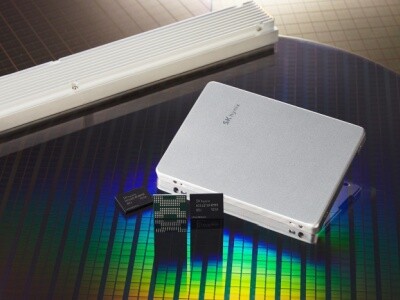

A Hynix a frissen bejelentett, lapkájával új generációs UFS 3.1-es adattárolókat tervez, amelyek a következő évben utat találhatnak az okostelefonokba, emellett 2 TB-os végfelhasználói, illetve 16-32 TB-os adatközpontokba szánt SSD-k is érkezhetnek a vállalat portájáról.

A tömeggyártás hamarosan megkezdődik, emellett a vállalat annyit elárult, hogy dolgoznak egy 172 cellaréteget használó verzión is, amely valószínűleg majd jövőre lesz elérhető.