Az Intel új, 22 nm-es gyártástechnológián készülő, Ivy Bridge kódnevű lapkájáról már két nappal ezelőtt is érkeztek adatok, ám most a vállalat a hivatalos bemutató keretében is lerántotta a leplet a főbb újításokról. Ezek egy részét nemrég megjelent hírünkben megírtuk, de ma is sok újdonság látott napvilágot, így érdemes a témát még tovább ragozni, és szót ejteni az eddig nem említett dolgokról. Elsőként le kell szögezni, hogy az Ivy Bridge legnagyobb előnye, hogy egy heterogén módon programozható lapkáról van szó, ami a Sandy Bridge-ről nem mondható el. Ezzel lényegében az Intel követi az AMD-t az APU-k világába, ami várható lépés volt, hiszen nem kérdés, hogy a szoftverek fejlesztése is erre tart.

Az alapok a Sandy Bridge-hez képest gyakorlatilag nem változtak, vagyis a rendszer lelke továbbra is a nagyméretű L3 gyorsítótár, amire négy processzormag és egy grafikus mag van felfűzve. Az Ivy Bridge továbbra is a MESIF koherencia-protokollt alkalmazza, vagyis az L3 cache négy részre van osztva, és egy gyűrűs busz köti össze ezeket. Mindegyik processzormag írhatja a saját L3 részterületét, olvasáskor viszont az egyes magok a teljes gyorsítótárat elérik. Az IGP továbbra is írhat a teljes L3 cache-be, vagyis a Sandy Bridge-hez képest itt sem változott a helyzet. A rendszer működését ebből a szempontból a fent linkelt hírben részleteztük.

Valójában ez a koncepció jó is, meg rossz is. Jó, ha az adott program fejlesztője kontrollálja az IGP írását a harmadszintű gyorsítótárba, hiszen így az adatok egyszerűen megoszthatóak a processzormagok és a grafikus processzor között. Rossz, ha ez a kontroll a szoftver oldaláról nem történik meg, ugyanis az IGP szálanként nem kevés területet (a Sandy Bridge esetében 32 kB) szerezhet, vagyis a gyorsítótár nagy részét egyszerűen teleszemeteli, ami akadályozza a processzormagok normális működését, és ez sebességvesztéshez vezet. A probléma súlyossága szoftvertől függ, de helyenként nagyon lecsökkenthető a rendszer sebessége, ami ellen az Intel már a Sandy Bridge-hez írt driverekben is védekezett, vagyis a problémás alkalmazásoknál letiltották az IGP L3 cache-be való írási jogát. Valószínűleg az a módszer él majd az Ivy Bridge esetében is, ugyanakkor az egész kiegészül egy dedikált gyorsítótárral, ami a ROP-blokk mellett lesz. Ez előnyt jelent, ha az adott szoftverben az L3 cache-be való írási jogát tiltani kell, ám az Intel nem akarja, hogy az IGP teljesítménye ettől összeomoljon. Tulajdonképpen egyfajta dedikált gyorsítótárról van szó a grafikus magon belül.

Az Ivy Bridge IGP-je (forrás: AnandTech) [+]

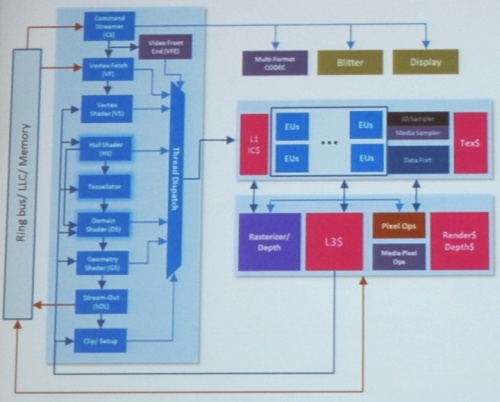

Ahogy arról már voltak pletykák a legnagyobb változáson nem a processzormagok, hanem az IGP ment keresztül. A rendszer sok szempontból megújult, és jobban lehet skálázni is. Az Ivy Bridge grafikus magja egy shader tömböt használ az adatok feldolgozására, melyen belül 16 darab shader processzor található, amit az Intel Execution Unit néven emleget. Ezek lényegében széles vektorfeldolgozók, és támogatják a bitszintű utasításokat, valamint az IEEE754-2008-as lebegőpontos szabványt. Mivel az IGP megfelel a DirectX 11-es API követelményeinek, a Local Data Share funkció is megtalálható, amit a Santa Clara-i óriáscég valamiért Shared Local Memory jelzéssel illetett, de lényegében a shader tömbben található L1 gyorsítótárról van szó, amelyen belül a shader processzorok megoszthatják az adatokat.

A textúrázó blokk szintén a shader tömb része, ám arról nincs pontos információ, hogy hány csatorna áll majd rendelkezésre, továbbá a ROP blokkal kapcsolatban is csak annyit tudni, hogy egy darab található az IGP-ben. Feltételezhetően a shader tömb nyolc darab Gather4-kompatibilis textúrázó csatornát tartalmaz, míg a blending egységek száma négy lesz. A setup részen belül az Intel fix funkciós tesszellátort alkalmaz a tesszellálásra, továbbá a vállalat a geometry shaderek esetében elérhető teljesítményt is növelte a dedikált stream output egységgel. Ezt a funkciót a Sandy Bridge is támogatta, de csak emulált formában. A DirectX 10.1 API a specifikációk alapján erre lehetőséget ad, de borzalmasan lassú megoldásról van szó, így célszerű volt bevezetni egy fejlettebb, és jóval gyorsabb megvalósítást.

Az AMD Llano és az Intel Sandy Bridge anizotropikus szűrésének mintavételezési képessége (forrás: The Tech Report) [+]

A Sandy Bridge IGP-jét a 3D-s alkalmazások képminőségének vizsgálatánál is nagyon sok panasz érte. A HD Graphics 2000 és 3000 az anizotropikus szűrésre egy nagyon régi szögfüggő algoritmust használt, amilyennel még 2001-ben találkozhattak a felhasználók a Radeon 8500 és a GeForce 3 sorozatban. Nem kérdés, hogy egy közel 10 éves szűrési megoldás már nem elég fejlett ahhoz, hogy felvegye a versenyt az élmezőnnyel, ami sajnos meg is látszott a képminőségen. Az Intel az Ivy Bridge esetében ezen javítani fog. Hogy mennyit, azt még nem tudni, de minden előny jól jön, hiszen az aktuális széria az anizotropikus mintavételezés szempontjából nagyon gyenge munkát végez a közvetlen konkurensnek számító AMD Llano APU-hoz, vagy az aktuális Radeon és GeForce kártyákhoz viszonyítva.

Az AMD Llano és az Intel Sandy Bridge anizotropikus szűrésének minősége a Portal 2-ben (forrás: The Tech Report) [+]

Az új IGP extrája még, hogy képes három független kijelző natív kezelésére. Ezzel az Intel az AMD Eyefinity szolgáltatására kíván válaszolni, mely az üzleti termékek esetében nagyon kedvelt. Az még kérdés, hogy az AMD a Trinity APU-ban bevezeti-e a három monitor kezelését, ugyanis ez a fajta extra szolgáltatás – hivatalos támogatás mellett – jelenleg egy dedikált Radeon GPU-t, vagy esetlegesen egy SLI-be kötött GeForce konfigurációt követel.

A processzormagok oldaláról már jóval kevesebb a változás. Az Intel valamelyest növeli az IPC-t, azaz az egy órajel alatt elvégzett munkát, emellett a további funkciók főleg biztonságra helyezik a hangsúlyt. Integrálásra kerül egy véletlenszám-generátor és az SMEP (Supervisory Mode Execution Protection). Előbbi egységhez új utasítások kerülnek bevezetésre, és a rendszer a másodpercenként több gigabit véletlenszerű adatot generál. Az utóbbi funkció azokat a támadásokat akadályozza meg, melyek a jogosultság kiterjesztésére irányulnak. Ezzel a rendszer biztonságosabb lesz. A támogatás valószínűleg nem csak a hardver oldalról szükséges, így az operációs rendszert is frissíteni kell, de erről az Intel még nem közölt hivatalos adatot.

A memóriavezérlő is fejlődött, ugyanakkor marad kétcsatornás kiépítés. Az új egység hivatalosan támogatja a DDR3L memóriaszabványt, azaz képes az 1,35 V-os memóriák kezelésére, továbbá a maximálisan támogatott effektív memória-órajel értéke 2133 MHz-re nőtt, ami a DDR3 szabványban specifikált legmagasabb érték jelenleg. Természetesen tuning mellett nagyobb órajel is beállítható, de ezt már több platformnál megszokhatták a felhasználók.

(forrás: AnandTech) [+]

Az egyik dián feltűnt még egy értékes információ, mely az Ivy Bridge kompatibilitásáról informálja a médiát. A termékről régóta tudható, hogy LGA1155-ös tokozást kap, amit a Sandy Bridge is használ, de a régi alaplapok támogatásáról még nem közölt hivatalos információt az Intel. Ennek most vége, ugyanis az Ivy Bridge APU logikai működését tárgyaló vázlatában egy 2011-es PCH van megemlítve, vagyis megoldható a támogatás a 6-os szériás vezérlőhidakkal. Ennél pontosabb adat nincs, de ez már valamilyen szinten bíztatónak számít.