Voltába oltott Turing

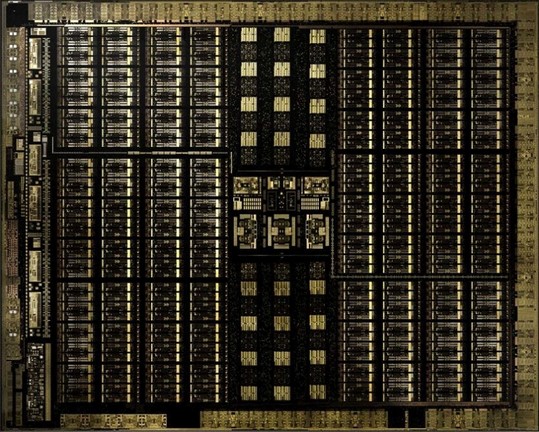

Az NVIDIA nagyjából egy hónapja jelentette be az új GeForce-ok érkezését, amelyek előrendelhetők is voltak, de a konkrét startra várni kellett, illetve a tesztek is csak később jelenhetnek meg, viszont a hardverek nyers paraméterei bemutathatók. A vállalat három darab lapkát tervezett az új GeForce és Quadro sorozatba, ezek a TU102, TU104 és TU106 kódnevet viselik. Mindegyik a TSMC 12 nm-es FFN node-ján készül, és rendre 18,6, 13,6, illetve 10,6 milliárd tranzisztorból épülnek fel, miközben a kiterjedésük 754, 545 és 445 mm². Ebből látható, hogy a legkisebb is kifejezetten nagy, ezért sincs igazán olcsó verzió, így a korábbi, Pascal architektúrára épülő GeForce-ok a piacon maradnak.

A Turing architektúra leginkább a Volta továbbfejlesztésének tekinthető. A streaming multiprocesszorok általános felépítése az alapvető működést tekintve nem sokat változott, leginkább kiegészült bizonyos képességekkel, illetve az RT maggal, legalábbis ennek egy multiprocesszorra levetített részével. Az ehhez kapcsolódó képességről korábban írtunk, és azóta sincs sokkal több adat, de ugye még nem érkezett meg a Windows 10 új frissítése, ami hozza majd a működéshez szükséges DirectX Raytracinget, így erre később vissza lehet térni. A DLSS-ről sincs sok új információ, ennek a működését is leginkább meg kell nézni a gyakorlatban.

A Turing multiprocesszorokon belül marad a négy compute blokk. Ezeken belül marad az egy feladatirányító (dispatch) és az egy warp ütemező, amelyek többféle futószalagot etetnek. Az NVIDIA – szokás szerint – még ma is használja a CUDA mag kifejezést, de ennek a Turing esetében sincs igazán értelme, mivel már nem komplex feldolgozók találhatók a blokkokon belül. Ennek megfelelően a Turing architektúrában – a Voltához hasonlóan – az utasításszavak végrehajtása a nekik megfelelő futószalagon történik. Ha 32 bites lebegőpontos operációról, azaz FP32-ről van szó, akkor egy darab 16 utas, 32 bites integer, azaz INT32 mellett egy darab szintén 16 utas, míg a Tensor műveleteknél egy darab 128 utas tömb áll rendelkezésre. Utóbbi esetben fontos kiemelni, hogy ezek strukturálva vannak, vagyis egy 128 utas tömb gyakorlatilag két darab úgynevezett tensor magot jelent, amelyek 64-64 darab ALU-t használnak. Alapvető újítás a Volta architektúrához viszonyítva, hogy a Turing képes az INT32 és az FP32 feldolgozók egyszerre történő használatára. Ez igazából egy elméleti képesség, valójában még mindig az határozza meg a gyakorlati használhatóságot, hogy van-e elég szabad regiszter annyira sok warpot futtatni, hogy ezek száma át tudja lapolni a memóriaelérés késleltetését.

Az NVIDIA CUDA magoknak az FP32-es ALU-kat tartja, ami nem túl kedvező állásfoglalás, hiszen korábban ez egyszerre jelentett lebegőpontos és integer ALU-kat, de ez legyen a legnagyobb probléma. Az FP32 ALU-k az IEEE754-2008-as szabványnak megfelelők, és támogatják a MAD (Multiply-Add), illetve az FMA (Fused Multiply-Add) instrukciókat, valamint az FP16-os műveleteket is, méghozzá úgy, hogy egy FP32-es feldolgozó két darab, egymástól nem függő 16 bites lebegőpontos operációt hajthat végre. A load/store egységek bekötése másolja a Volta dizájnját, de változás, hogy ezek száma felére csökkent, változatlanul marad viszont a trigonometrikus és transzcendens utasítások végrehajtásáért felelős speciális funkciókat biztosító egység (SFU). Ez a Pascal architektúrához viszonyítva már nem végez interpolációt, mivel azt a Voltához hasonlóan a Turing is manuálisan oldja meg. Utóbbi egy fontos változás, ugyanis a baricentrikus koordináták kiolvasását már szabványosította a Microsoft a shader modell 6.1-ben, így mindenképpen a manuális interpoláció a nyerő.

A compute blokkokon belüli regiszterterület marad 64 kB, vagyis annyi, amennyi a Voltában volt. A textúrázási képességek területén sincs igazán újítás. Az egyes streaming multiprocesszorok egy darab, négy csatornát biztosító textúrázó blokkot tartalmaznak, amelyet négy compute blokk használ egyszerre.

A cikk még nem ért véget, kérlek, lapozz!