A Piledriver modul újításai

Az AMD az elmúlt év elején kezdte meg fúzióját, méghozzá a Brazos platformmal. A rendszer mára a vállalat történelmének legkelendőbb megoldásává lépett elő, ám a nagyobb verziónak felfogható Llano APU a kezdeti ellátási problémák miatt már nem teljesített ilyen jól. Az ellátás normalizálása mellett a termékre az elmúlt két negyedévben nagyon fellendült a kereslet, de ez már nem sokat számít, hiszen elérkezett az idő az utód bemutatására.

Az új generációs Trinity APU az AMD második nekifutása a fúzió projekten belül, és a cég útiterve szerint az optimalizált integrációt valósítja meg. Mint ismeretes, az első lépcsőben még csak a fizikai integráció jelentette a célt, ami meg is valósult, míg a második lépcsőfok tulajdonképpen a teljesítmény növelésére, illetve a fogyasztás csökkentésére figyel. Elöljáróban annyit, hogy ezek szintén megvalósultak, sőt, némi extrára is futotta.

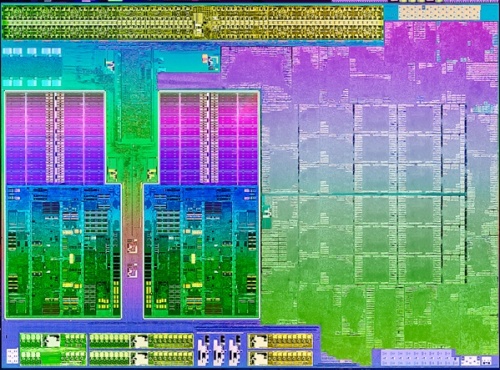

A Trinity APU kiterjedése 246 mm², a lapka pedig 1,303 milliárd tranzisztorból épül fel. Rögtön észrevehető, hogy a tranzisztorszám csökkent a Llano APU-hoz képest, de ez a valóságban nem ilyen egyszerű. Úgy néz ki, hogy az AMD áttért a sematikus adatokra, azaz nem valós tranzisztorszámot ad meg a cég. Ennek megfelelően átszámították a Llano APU korábbi tranzisztorszámát is, mely így 1,178 milliárd lett. Ugyanez okozta a Zambezi kódnevű processzor esetében a félreértéseket, amikor az AMD 1,2 milliárd tranzisztorra módosította az eredetileg 2 milliárd tranzisztoros értéket. Technikailag mindkettő helyes, ugyanis itt arról van szó, hogy a sematikus dizájn tervezésénél adott egy tranzisztorszám, de a konkrét fizikai implementáció során előfordulhat, hogy hatékonyabb az adott áramkört több tranzisztorból építeni. Az eltérés mértéke nagyban függ az adott chipdizájntól, illetve a mérnökök döntésétől, így erre nincs konkrét szabály, de biztos, hogy a sematikus tranzisztorszám nem lehet nagyobb a valósnál. Mindez persze lényegtelen, mivel a lapkák tényleges működésén nem változtat, a vásárlókat pedig jellemzően nem érdekli a gyártástechnológia és a tranzisztorszám.

Az AMD Trinity APU

A Trinity a Llano APU-hoz hasonlóan 32 nm-es SHP gyártástechnológiával készül, ám a lapka processzor része, valamint az IGP már gyökeresen eltér. Stílszerűen kezdjük az elemzést a processzormagok, pontosabban modulok oldaláról. A Llano ebből a szempontból viszonylag régi architektúrára épült, de a Trinity már a Bulldozer továbbfejlesztésének tekinthető Piledriver modult veti be. Korábban már leírtuk, hogy az egész fejlesztés koncepciója az egyszerűsítés, és ez most sem változott. A kiindulási pont két teljes értékű mag volt, melyet az AMD egy modullá vont össze. Ez két darab integer magból, és egy megosztott lebegőpontos egységből áll.

Az elgondolás alapján a modulon egy-egy szál fut az integer magokon, és a Flex FP névre keresztelt lebegőpontos végrehajtó közös. Utóbbi működésében van a csavar, ugyanis az integer magok megfelezhetik a megosztott erőforrást, vagy az egyik mag teljesen ki is sajátíthatja azt, esetlegesen az is előfordulhat, hogy a munkafolyamathoz nem szükséges a Flex FP használata, így a teljes erőforrás lekapcsolható, ezzel pedig növelhető az integer magok órajele. A Flex FP lényegi előnye tehát a flexibilis működés, ugyanis ezzel a koncepcióval az AVX használata nélkül is kihasználható a feldolgozómotor 256 bites szélessége. Tudniillik a lebegőpontos feldolgozók egyszeres (32 bites) és dupla (64 bites) pontosságú utasításokkal dolgoznak. Lehetőség szerint annyit hajtanak végre, amennyi belefér a megadott hosszúságú egységbe. Ebbe sajnos beleszól az utasításkészlet is, ugyanis csak az AVX támogatja a 256 bites feldolgozást, ami azt jelenti, hogy egy AVX-et nem támogató programnál a 256 bites lebegőpontos végrehajtó 128 bitesként működik. Az AMD moduláris megvalósítása erre a problémára megoldást jelent, és az architektúra az alkalmazás újrafordítása nélkül képes kamatoztatni a két darab 128 bites FMAC egységet. Ez a gyakorlatban azt jelenti, hogy a 128 bites feldolgozást támogató SSE utasításkészlet maximálisan ki tudja használni az adott processzormodul hardveres képességeit. Ez a dedikált ütemezőnek hála, akkor is él, ha a modulon belül az egyik integer mag teljesen kisajátítja a lebegőpontos feldolgozót. A modulban a magok természetesen megosztják az információkat, és a rendszer még végrehajtás előtt képes elemezni a feladatot, vagyis előre el tudja dönteni, hogy a 256 bites lebegőpontos feldolgozót megossza, vagy hozzárendelje az egyik integer maghoz.

Rögtön látható, hogy a Llano APU-hoz képest a Trinity már modernebb lebegőpontos motorokkal és integer magokkal rendelkezik, így az új utasításkészletek támogatása is megoldható. Ez olyannyira igaz, hogy a Trinity előlépett a piac legokosabb x86 kompatibilis termékévé, hiszen az AMD64-es kiterjesztés és az MMX, SSE, SSE2, SSE3, illetve SSE4A mellett a rendszer kezeli az SSSE3, az SSE4.1, az SSE4.2, az AVX, az AES, az FMA4, az XOP és a PCLMULQDQ utasításkészleteket. Itt még fontos adalék, hogy a sűrűn használt PREFETCH és PREFETCHW utasítások – a 3DNow! támogatás megszüntetése után – továbbra is elérhetők egy 3DNowPrefetch csoportban.

Kiemelendő a Piledriver modulok esetében a BMI (Bit Manipulation Instructions) és a TBM (Trailing Bit Manipulation) utasítások támogatása, melyekkel az AMD már készül a GCN architektúra beköltöztetésére. Emellett az új processzormodul két új utasítást (VCVTPH2PS és VCVTPS2PH) kínál a 16 bites félpontosságú és a 32 bites egyszeres pontosságú lebegőpontos számok közti konvertáláshoz, melyek a nemrég megjelent Ivy Bridge-ben mutatkoztak be. A nagy újdonság azonban az FMA3 utasítás támogatása, mely kompatibilis lesz az Intel későbbi termékeiben bevetésre kerülő verzióval.

A helyzet itt érdekes, ugyanis az AMD az FMA3 mellett az FMA4-et is megtartja. A különbség a regiszterek kezelésére van hatással. Az FMA4 az összes operandushoz külön regisztert használhat, míg azt FMA3 esetén az eredmény a három operandushoz használt regiszterek közül az egyikbe kerül. Apró eltérésről van szó, de ez már elég ahhoz, hogy a két utasítás ne legyen kompatibilis egymással. Ez a fejlesztők számára komoly probléma. Az FMA4 a programozás kényelmessége szempontjából sokkal előnyösebb, mivel nem ritka, hogy egy programon belül többször is szükség van ugyanazokra az értékekre, ám az FMA3 esetében ez alapvetően nem lehetséges, hacsak a felülírandó regiszter tartalmát a programozó nem másolja másik regiszterbe, vagy ha nincs már szabad kapacitás, akkor újra be kell olvasni a memóriából vagy a gyorsítótárból, ami jelentősen lassítja a munkavégzést. A kompatibilitás viszont az FMA3-ra lesz megoldva, így a fejlesztőknek meg kell barátkozni ezzel a helyzettel.

A Piledriver modul egyébként több részen is változik a Bulldozerhez képest. Az AMD rengeteg helyen optimalizálta az architektúrát, így az új processzormodul integer magjainak L1 adat TLB mérete 32-ről 64 bejegyzésre nő, emellett javul a Flex FP motor és az integer magok ütemezése, 44 eleműre nő a magonkénti olvasási sor, pár utasítás feldolgozása gyorsul. Hatékonyabb lesz az elágazásbecslés, az adatok előbetöltése, illetve az L2 gyorsítótár működése is. Összességében az AMD ezzel növelte az IPC-t, vagyis az egy órajel alatt végrehajtható utasítások számát. A Piledriver modul számottevő újítása még, hogy beveti a Cyclos Semiconductor Resonant Clock Mesh (RCM) nevű eljárását, mellyel a fogyasztás csökkenthető, amellett, hogy a beállított órajel igen magas lehet.

A cikk még nem ért véget, kérlek, lapozz!