A Samsung már korábban bejelentette, hogy tervezik a 3 nm-es node-jukat, amelynél a FinFET tranzisztorstruktúrát a GAAFET fogja váltani. Az utóbbi, Gate All Around FET, azaz nanohuzalos technológiára a skálázhatóság megőrzése miatt van szükség, mivel a 3 nm-es csíkszélesség már túl kicsi lesz ahhoz, hogy a FinFET működjön.

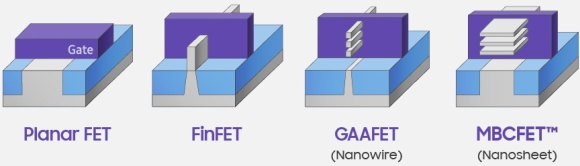

A problémát a source és drain közötti, kikapcsolt állapotban jelentkező elektronszivárgás okozza, ugyanis ezek minden egyes csíkszélességváltással egyre közelebb kerülnek egymáshoz, vagyis az úgynevezett short-channel effect hatása fokozódik. Lényegében a FinFET is emiatt lett bevezetve anno, mivel a mérnökök rájöttek, hogy ha a source és a drain kiemelkedik az alaprétegből a szigetelő fölé, akkor körbe tudják fogni a kapuelektródával, így jobban tudják kontrollálni a short-channel effect problémáját. De ez is csak egy bizonyos mérethatárig működik, és 3 nm-en már eljön az az abszolút minimum szint, amikor már egyéb technológiákkal sem skálázható tovább a FinFET. A GAAFET itt jön képbe, ugyanis ennél a megoldásnál a source és a drain közé nanohuzalok kerülnek, amiket teljesen közrefog a kapuelektróda, leszigetelve azokat. A nanohuzalok száma változó lehet, az ábrán szereplő háromnál több is bevethető, de ezek már egyéni döntések, amelyeket a félvezetőgyártók az adott eljárásaiknak megfelelően hoznak majd meg.

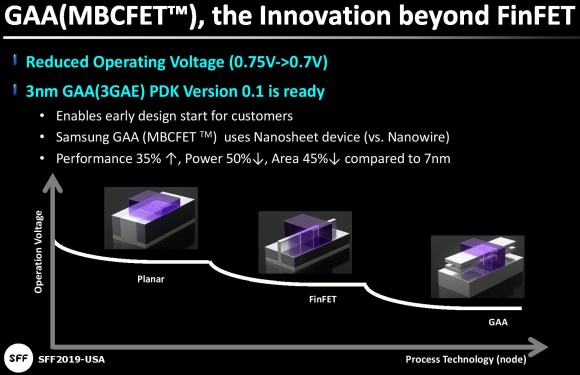

A GAAFET struktúrának több formája is lehet, a nanohuzalok helyett például alkalmazhatók nanolapok is, amit a Samsung MBCFET, azaz Multi-Bridge Channel FET néven emleget. Ezt a verziót veti be a cég a 3 nm-es, 3GAE nevű node-jánál, és a nanolapok szélességének módosításával a partnerek némi flexibilitást kapnak a dizájnjaik kialakításánál. Mindemellett az MBCFET nagymértékben kompatibilis a FinFET eljárásokkal, így a meglévő technológiák és berendezések újrahasznosíthatók, ami felgyorsítja az új gyártástechnológia bevezetését.

A Samsung a Foundry Forum rendezvényen részletezte, hogy a 3GAE nevű eljárással az üzemfeszültség 0,7 V-ra csökkenhet, a teljesítmény pedig 35%-kal lehet jobb a 7 nm-es node-jukhoz viszonyítva, miközben az adott lapka fogyasztása a felére csökken, a lapkaterület pedig 45%-kal mérséklődik.

A Samsung már ki is adta a Product Design Kit 0.1-es verzióját, amivel a partnerek megkezdhetik a 3 nm-es dizájnok tervezését. Az új gyártástechnológia bevezetésére továbbra is leghamarabb 2022-ben lehetséges.