A Zen mélylélektana

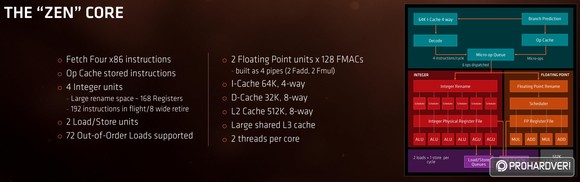

Magába a Zen magba beférkőzve rögtön megemlíthető a rendkívül kigyúrt front-end rész, amelyben felfedezhető a µop cache. Az AMD-nek ez az első processzora, amelyben ezt beveti. A µop cache egyébként legelőször az Intel Sandy Bridge magban jelent meg, és a legfőbb célja a teljesítmény növelése, illetve a fogyasztás csökkentése.

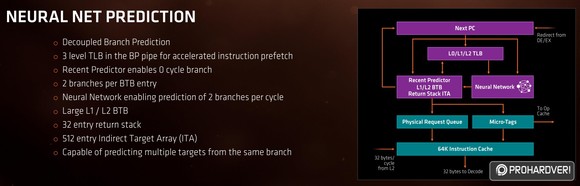

A Zen magon belül az utasításablak 64, míg az utasításbetöltés 32 bájtos, az elágazásbecslés pedig teljesen dinamikus. Ezen a ponton erős az AMD újdonsága, amit a cég szimplán Neural Net Prediction néven emleget. A működés során a feltételes elágazásoknál a hash perceptron, illetve újabban már a Neural Network nevű egység ellenőrzi a kétszintű, azaz L1 és L2 branch target buffert (BTB). Ezek a Jaguar magból ismerősek lehetnek, és ezúttal is gyorsítótársoronként két elágazás tárolható, a Neural Network egység így órajelenként két elágazásról tud dönteni. Bár az L1 és L2 BTB-k méretét az AMD nem adta meg, az biztos, arra vonatkozóan van utalás, hogy ezek nagy kapacitásúak.

A Zen mag egy közvetett elágazás detektálása után beveti az ITA-t, vagyis az Indirect Target Array egységet, aminek az 512 bejegyzési helyének egyikére kerül az elágazás, ami után a 32 bejegyzés tárolására alkalmas return stack lesz követve. A rendszer a hatékonyság növelése érdekében képes arra, hogy egy téves elágazás után a megfelelő elágazást tartalmazó szálnak prioritást adjon, így hamarabb lesz eredmény.

Jó hír, hogy a Zen magban már az utasítás translation lookaside buffer (iTLB) része az elágazásbecslésért felelős blokknak, ami szintén növeli a hatékonyságot. A háromszintű iTLB L0, L1 és L2 pufferrel rendelkezik, az első 8, a második 64, míg a harmadik 512 bejegyzést képes tárolni.

Rátérve az utasításbetöltésre és dekódolásra, a Zen 64 kB-os, négyutas, csoport asszociatív utasításgyorsítótárt kapott, míg a dekódertömb négy darab x86-os utasítást képes beolvasni egyszerre, és a dekódolás után maximum 8 µop állítható elő. Ezek a 72 bejegyzéses, szálak között statikusan particionált µop parancslistába kerülnek.

A Zen mag a valós végrehajtás tekintetében egy integer és egy lebegőpontos részre oszlik. Az integer részen belül négy ALU (aritmetikai-logikai egység) és két AGU (címgeneráló egység) található. Az ALU-k mindegyike képes alapvető integer operációkra, illetve a shift, valamint a kétoperandusos LEA (load effective address) utasításra. Két ALU tud branchet futtatni, míg egy-egy ALU képes szorozni és osztani. A háromoperandusos LEA már az AGU-kon futtatható. A lebegőpontos részen két darab 128 bites FMAC egység található, amelyek egy-egy 128 bites FMA operációt, vagy egységenként egy 128 bites ADD és egy 128 bites MUL operációt tudnak elvégezni. Az L1 gyorsítótár 32 kB-os nyolcutas, csoport asszociatív.

A Zen az utasításkészletek szempontjából tulajdonképpen mindent támogatni fog, amit ma egy processzor támogathat. Ebbe beletartoznak az elterjedt, szabványosnak tekinthető utasításkészletek, illetve a viszonylag sűrűn használt utasítások is. Két újítást kínál azonban az AMD, amelyek közül az egyik a CLZERO. Ennek segítségével kitörölhető egy 64 byte-os gyorsítótársor (cache line), ami különösen hasznos lehet az adatközpontokban és a HPC szerverekben. A másik újítás a PTE (Page Table Entry) Coalescing, ami igazából nem is utasítás, hanem sokkal inkább egy funkció, és nem szükséges speciális szoftvertámogatás a működéséhez. Ez annyit tesz, hogy a 4 kB-os laptáblákat összeállítja 32 kB-osokká, ezzel hatékonyabban használhatók fel a címfordítási eredményeket tároló TLB (Translation Lookaside Buffer) slotok. Ugyanakkor a PTE Coalescing működéséhez számos feltételnek kell teljesülni, de ha ez megvan, akkor a rendszer beveti a technikát.

A cikk még nem ért véget, kérlek, lapozz!