Haswell (22 nm)

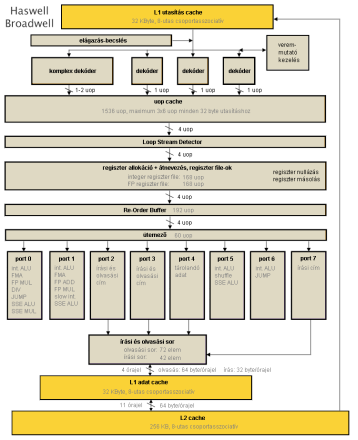

Megszokottnak nevezhető, hogy a generációról generációra finomított elágazásbecslés mellett a fejlettebb gyártástechnológiából származó tranzisztorbüdzsé egy részét az out-of-order végrehajtást biztosító, illetve elősegítő pufferek növelésére költik. A Re-Order Buffer (azaz előrelátási ablak), az ütemező és az L1 cache-t tévesztő memóriaolvasási és -írási műveletek sorai mind-mind folyamatosan nőttek a nagyobb (tock) mikroarchitektúra-váltások során, és a jövőben is gyarapodni fognak: ezeknél a puffereknél a végtelen méret lenne ideális, tehát növelésük útjába nem áll praktikus akadály, csak 5-10 bájt nagyságrendű elemméretük és a hozzájuk tartozó vezérlőlogika tranzisztorigénye. A Haswell esetében a ROB (Re-Order Buffer) a Sandy és Ivy Bridge esetében rendelkezésre álló 168-ról 192 µop-ra nőtt.

Mivel az első- és másodszintű gyorsítótárak méretét a Nehalemmel kvázi bebetonozták, ezért a hozzájuk vezető adatút szélességének növelése kritikus a végrehajtó egységek megfelelően ütemezett adatokkal való ellátásának szempontjából. A Haswell immár 2 x 256 bitet olvashat ki órajelenként az L1D-ből, továbbá az L2-ből az L1 cache-be is órajelenként 64 bájtot (azaz egy teljes cache-vonalat) mozgathat.

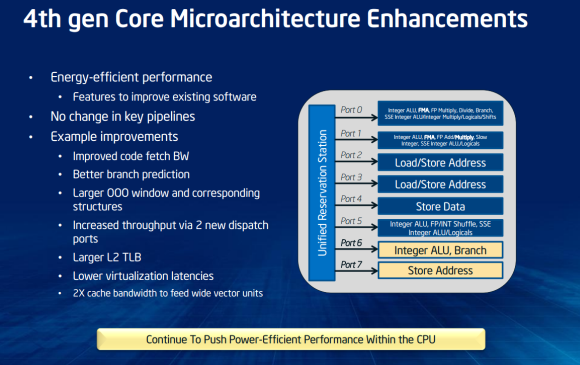

Hosszú idő után bővülést láthatunk a végrehajtó egységek számában: az Intel a Core 2 processzorok megjelenése óta az Ivy Bridge-ig bezárólag 6 műveletvégző egységgel operált, amelyek szerepköre ugyan változott az idők folyamán, de alapvetően a következő felosztás általánosan igaz:

- 3 műveletvégző egység (port 0, 1 és 5);

- 2 címszámító egység (port 2 és 3);

- 1 adattárolási egység (port 4).

A Haswell két további porttal bővíti a repertoárt: egyrészt a két címszámító mellé egy harmadikat (port 7) is alkalmaz, kifejezetten a tárolási műveletek címszámításainak részére, így a másik kettő elláthatja beolvasott adatokkal a két 256 bites lebegőpontos egységet (port 0 és 1), valamint az új 6. portot kifejezetten egyszerű integer műveletek részére tartja fenn, biztosítva, hogy a SIMD-ciklusok végrehajtása közben a mutató-, számláló- és ciklusműveletek ne vegyék el az erőforrásokat a vektorműveletektől. Ezen új portok jótékony hatása az egyszálas végrehajtásnál is tetten érhető, de a Hyper-Threading által lehetővé tett kétszálas működésnél mutatkozik meg igazán.

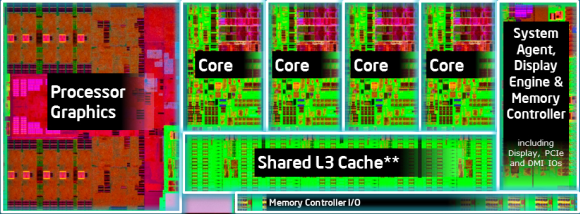

A négymagos Haswell felépítése [+]

A mikroarchitektúra módosítása mellett új utasításkészletek is költöztek a processzorba, a választék bővítésének tekintetében viszont a Haswell kiemelkedik a korábbi generációk közül.

Tranzakcionális memóriakezelés

Azon többszálú programoknak, amelyek nem statikusan felosztott adathalmazokon dolgoznak – pl. 2 mag esetén az adatok felén, 4 mag esetén a negyedén stb. –, általános problémája annak biztosítása, hogy ugyanazt az adatot egyszerre csak az egyik szál módosíthassa. Az x86/x64 architektúra az egyetlen egész számot tartalmazó változó közvetlen vagy akár feltételes atomi módosítására – amely lehet 1, 2, 4, 8 vagy 16 bájtos – kényelmes lehetőséget biztosít a LOCK utasításprefix vagy a CMPXCHG-utasításcsoport révén; előbbi a 'betöltés-módosítás-kiírás' típusú utasításoknál alkalmazható.

Amennyiben egynél több adat atomi módosítására van szükség, nehezebb a helyzet: ilyen esetben a teljes adathoz való hozzáférést egyetlen szinkronizációs változóval kell levédeni, ennek módosításáért (azaz birtoklásáért), majd visszaállításáért versengenek a szálak, és amelyik szál sikeresen módosítja a szinkronizációs változót, az hajthatja végre módosításait a teljes adathalmazon; a többi szál eközben várakozik tétlenül. Sűrűn előfordul azonban, hogy a különböző szálak adatmódosításai nem ütköznek egymással, általában más-más adatot módosítanak, így a várakozások nagy része felesleges lenne. E teljesítményromboló állási idők elkerülésére fejlesztették ki a tranzakcionális memóriakezelési technikákat, melynek első kereskedelmi forgalomba kerülő megvalósítása – mivel a néhai Sun Rock nevű processzort végül nem dobták piacra – a Haswellben debütál.

A Haswell rögtön két megoldást is kínál a tranzakciók kezelésére: az egyik teljesen kompatibilis a régebbi processzorokkal (HLE, Hardware Lock Elision) – bár hatása nem érvényesül azokon, de érvényes utasításként elfogadják őket –, a másik (TSX utasításkészlet) három új utasítás bevezetését jelenti: XBEGIN, XEND és XABORT. Mindkettő működési mechanizmusa azonos:

- a tranzakció elejét és végét egy-egy utasítás jelzi;

- a tranzakció végrehajtása közben a processzor feljegyzi, hogy mely memóriaterületekről történt olvasás és melyekre írás, valamint a módosítások csak az L1D és L2 cache-be kerülnek, miközben az L3 az eredeti adatokat tartalmazza, így a többi programszál ezeket látja;

- a tranzakció végén a processzor ellenőrzi, hogy a feljegyzett memóriaterületek még mindig az eredeti értékeket tartalmazzák-e (azaz amikkel a program a tranzakció alatt számolt, azt más szál nem módosította-e időközben); ha igen, akkor az adatmódosítások egyszerre lesznek láthatóak a teljes rendszer számára (commit); ha viszont változás történt, akkor az L1/L2 cache-ben levő a módosított értékeket felülírja az aktuális értékekkel (rollback), és újra megpróbálkozik a teljes tranzakció lefuttatásával.

Ily módon hardveresen biztosított az, hogy nem módosítja több szál egyszerre az adathalmaz azonos elemét, viszont figyelembe kell venni, hogy az adatmódosítások számának limitáló tényezője elsősorban a 256 kB-os L2 cache: túl sok felhasznált és/vagy módosított adat esetén a processzor önhatalmúlag megszakíthatja a tranzakciót (abort; erre a programozó is utasítást adhat bizonyos körülmények fennállása esetén); ilyen esetekre a TSX használatával külön 'menekülőút' írható a programba, míg HLE alkalmazása esetén újra lefut a tranzakció, immár az említett várakozás kikényszerítésével.

Bár a TSX minden Haswell lapkában megtalálható, a megjelenés után bő 1 évvel az Intel egy problémára hivatkozva az összes termékben letiltotta az utasításkészlet használatát.

A négymagos Haswell lapka felépítése [+]

FMA3

A Haswell megérkeztével az AMD után az Intel is bevezette a lebegőpontos FMA utasításokat (fused multiply + add), mégpedig háromparaméteres változatukat, amely egyik bemenő adatát felülírja az eredménnyel. Ezen 5 órajel alatt végrehajtódó utasítások 256 bites vektorokon is dolgozhatnak, továbbá órajelenként 2 kerülhet végrehajtásra, így – mivel egy FMA két FLOP-nak felel meg – az elődök 128, illetve 256 bites lebegőpontos végrehajtásához képest a Haswell 2-4-szeres elméleti számítási teljesítménynövekedést ígér.

AVX2

A Sandy Bridge-ben bemutatkozó, 256 bites vektorokon dolgozó lebegőpontos AVX utasítások után a Haswell AVX2 elnevezésű készletével az egész számos SIMD végrehajtást is kibővítette a korábbi 128-ról 256 bites vektorokra, leváltva/kiegészítve a koros 128 bites, Pentium 4-gyel bemutatkozó SSE2 készletet, valamint a Core 2 CPU-kban megjelent, ugyancsak 128 bites SSE4.1 egész számos SIMD-utasításainak nagy részét. Ennek előnyeit elsősorban a kép-, hang- és videófeldolgozó és -megjelenítő programok élvezhetik, de – tekintve az SSE2 mai elterjedtségét – számos különféle programban várható idővel a megjelenése.

Gather memóriaolvasás

Az eddigi x86/x64 SIMD műveletek végrehajtásához előre kellett gondoskodni arról, hogy a vektorok elemei egymás után sorakozzanak a memóriában, mivel egy-egy vektor egy folyamatos memóriaterületet jelent. A Haswellben bemutatkozó 'gather' típusú betöltési utasítás önállóan képes szétszórt elemekből összeállítani egy vektort, mivel paraméterként a kezdőcímet, valamint az elemek e címtől számított távolságát kapja meg. Bár technikailag ez a processzoron belül több külön memóriaolvasásként van megvalósítva, számottevően gyorsítja az ismétlődő minták szerinti memóriahozzáféréseket.

Bitmanipulációs utasítások

A Haswell új bitközpontú utasításokkal is gazdagodott, amelyek egész értékeken (szorzás, shiftelés/forgatás), illetve azok bitcsoportjain végzett bonyolult műveletek végrehajtását gyorsítja fel, külön utasításokként rendelkezésre bocsátva a korábban több instrukcióból álló műveletsorokat.

A cikk még nem ért véget, kérlek, lapozz!